Big Chip của Trung Quốc với 16 chiplet, 256 lõi có thể lách lệnh trừng phạt từ Mỹ với siêu máy tính và AI

Nhịp đập khoa học - Ngày đăng : 10:48, 17/01/2024

Big Chip của Trung Quốc với 16 chiplet, 256 lõi có thể lách lệnh trừng phạt từ Mỹ với siêu máy tính và AI

Một mạch tích hợp lớn được chế tạo từ toàn bộ đĩa bán dẫn silicon có thể là giải pháp của các nhà khoa học máy tính Trung Quốc khi tìm ra cách lách các lệnh trừng phạt từ Mỹ, đồng thời tăng hiệu suất bộ xử lý.

Mạch tích hợp (IC) là thành phần điện tử chứa nhiều linh kiện như transistor, điện trở và tụ trên một chip chất bán dẫn duy nhất. IC có thể thực hiện nhiều chức năng khác nhau, từ việc xử lý dữ liệu đến việc tạo ra tín hiệu điện tử. Các ứng dụng của IC rất đa dạng, từ bộ xử lý máy tính đến vi mạch điều khiển trong các thiết bị điện tử tiêu dùng.

Đĩa bán dẫn silicon (silicon wafer) là một đĩa silicon mỏng, thường có đường kính 200 mm hoặc 300 mm. Nó được sử dụng làm nền tảng để sản xuất các thiết bị bán dẫn, chẳng hạn IC, transistor và pin Mặt trời.

Bị hạn chế tiếp cận chip tiên tiến mới do các biện pháp kiểm soát xuất khẩu từ Mỹ, các nhà khoa học ở Trung Quốc đã phải suy nghĩ sáng tạo để phát triển siêu máy tính và trí tuệ nhân tạo (AI).

Cải tiến mới nhất là bộ xử lý (phiên bản đầu tiên có tên là Zhejiang) đang được phát triển bởi một nhóm từ Viện Công nghệ Máy tính (ICT), Viện Hàn lâm Khoa học Trung Quốc, do Phó giáo sư Xu Haobo và Giáo sư Sun Ninghui đứng đầu. Công việc của họ đã được trình bày chi tiết trong một bài báo được bình duyệt đăng trên tạp chí Fundamental Research.

Một bài báo đã được bình duyệt là được đánh giá bởi các chuyên gia trong lĩnh vực đó trước khi xuất bản. Quá trình bình duyệt nhằm đảm bảo rằng bài báo đáp ứng các tiêu chuẩn chất lượng cao về nội dung và hình thức. Các bài báo được bình duyệt thường được xuất bản trên tạp chí khoa học uy tín.

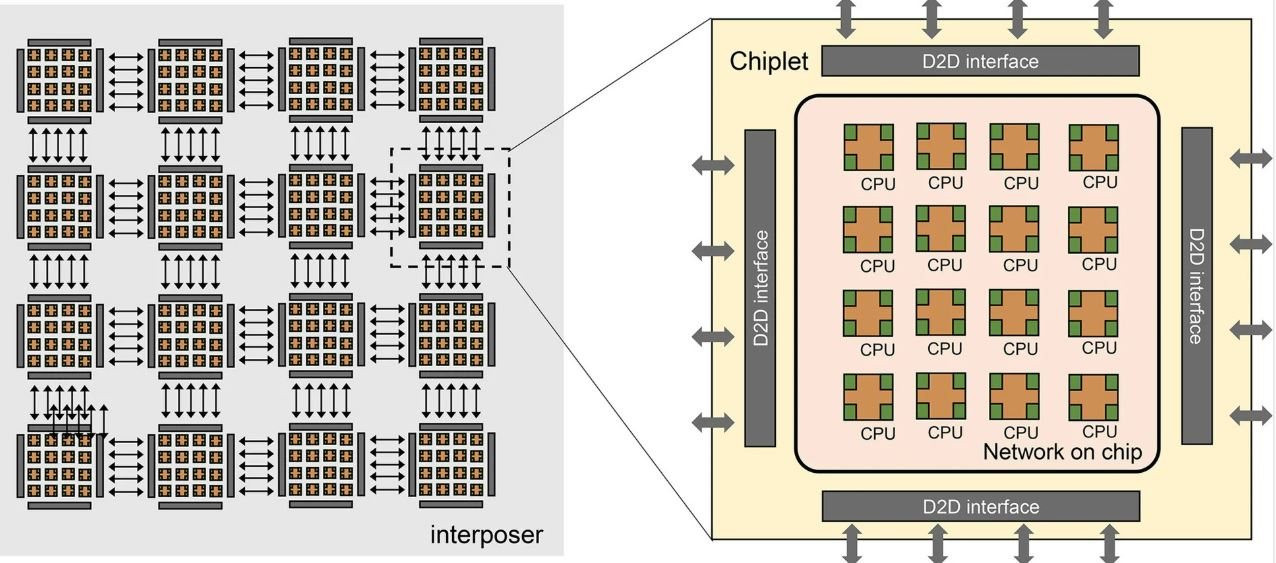

Zhejiang có diện tích hàng nghìn mm vuông, gồm 16 chiplet với 256 lõi. Các nhà nghiên cứu tiết lộ rằng Zhejiang có khả năng mở rộng tới 100 chiplet, tương ứng với tổng số 1.600 lõi.

Chiplet cho phép một khối IC được kết nối với các IC khác để tạo thành chip lớn hơn và phức tạp hơn. Chiplet được một số nhà nghiên cứu Trung Quốc coi là lựa chọn để nước này tạo ra con đường của riêng mình trong lĩnh vực sản xuất chip tiên tiến.

Theo các nhà nghiên cứu, Zhejiang có thể được sử dụng trong điện toán hiệu năng cao (HPC) và tăng cường đào tạo AI thế hệ tiếp theo.

“Khi định luật Moore đến hồi kết, việc triển khai các chip hiệu suất cao thông qua việc mở rộng quy mô transistor ngày càng trở nên khó khăn. Để cải thiện hiệu suất, việc tăng diện tích chip để tích hợp nhiều transistor hơn đã trở thành một cách tiếp cận thiết yếu”, Giáo sư CNTT Han Yinhe, tác giả đầu tiên của bài báo, viết.

Định luật Moore cho biết số lượng transistor trong một IC sẽ tăng gấp đôi cứ sau hai năm.

Để thiết kế chip có diện tích lớn hơn, phá vỡ các giới hạn về chi phí, năng suất và công nghệ in thạch bản, nhóm nghiên cứu đã đề xuất một dạng chip mới mà họ đặt tên là Big Chip.

Big Chip dùng để chỉ chip lớn hơn giới hạn diện tích của máy in thạch bản tiên tiến nhất hiện có. Nó có hai đặc điểm chính.

Đầu tiên, Big Chip thực sự rất lớn. Do kích thước lớn, Big Chip có thể chứa nhiều bộ phận điện tử nhỏ hoặc transistor hơn một chip thông thường được chế tạo bằng công nghệ hiện có.

Thứ hai, Big Chip có nhiều dies và một số kỹ thuật chế tạo chất bán dẫn mới nổi được sử dụng để tích hợp các dies chế tạo sãn sẵn vào Big Chip.

Dies thường được sử dụng để chỉ một phần nhỏ trên đĩa bán dẫn. Khi một đĩa bán dẫn được chế tạo, nó có thể chứa hàng ngàn hoặc thậm chí hàng triệu các thành phần điện được gọi là dies. Mỗi dies thường đại diện cho bản sao của một linh kiện hoặc một phần của chip. Khi đĩa bán dẫn được sản xuất, các dies sau đó được tách ra và sử dụng để tạo ra các chip cá thể.

Bao gồm hơn 1.000 tỉ transistor, Big Chip có thể được tạo ra bằng hai phương pháp.

“Phương pháp tiếp cận đầu tiên là tích hợp chiplet, bao gồm việc kết hợp nhiều chiplet trên chất nền trong một gói duy nhất. SoC (system on a chip) Kunpeng 920 của Huawei là ví dụ điển hình khi nó vẫn có kích thước của một CPU thông thường.

Phương pháp thứ hai là wafer-scale integration (WSI), liên quan đến việc xây dựng IC lớn từ một đĩa bán dẫn đầy đủ”, Han Yinhe cho biết.

SoC là kiểu kiến trúc trong công nghệ chế tạo bán dẫn, nơi một hệ thống hoàn chỉnh được tích hợp trên một chip duy nhất. Một SoC gồm tất cả thành phần cần thiết để hoạt động một hệ thống điện tử, chẳng hạn như vi xử lý trung tâm (CPU), bộ nhớ, điều khiển đầu vào/ra, trình điều khiển đồ họa và các thành phần khác.

Các ứng dụng của SoC rất đa dạng, từ điện thoại di động, máy tính bảng, đồ điện tử tiêu dùng đến các thiết bị nhúng và thiết bị IoT (Internet of Things). Bằng cách tích hợp nhiều chức năng vào một chip duy nhất, SoC thường giúp giảm kích thước, chi phí và tiêu thụ năng lượng so với việc sử dụng nhiều chip riêng lẻ.

Với WSI, bộ xử lý Zhejiang được thiết kế và chế tạo trên quy trình CMOS 22 nanomet. CMOS 22 nanomet là quy trình chế tạo mà công nghệ sản xuất các linh kiện trên một đĩa bán dẫn với độ chia tách của các dải dẫn transistor là khoảng 22 nanomet.

Vì Big Chip chứa nhiều lõi hơn nên sự giao tiếp giữa các lõi sẽ ảnh hưởng đến khả năng hợp tác của chúng, do đó thiết kế kiến trúc chip có tác động đáng kể đến hiệu suất.

Cerebras System, công ty AI của Mỹ, cũng sử dụng WSI để chế tạo chip có diện tích lên tới 46.225 mm2. Họ đã triển khai Wafer-Scale Engine-1 (WSE-1) vào năm 2019 và Wafer-Scale Engine-2 (WSE-2) trong năm 2021.

Một hệ thống hoàn chỉnh chứa WSE-1 đã được bán cho Trung tâm Siêu máy tính Pittsburgh và Quỹ Khoa học Quốc gia Mỹ vào năm 2020 để xây dựng siêu máy tính AI mang tên Neocortex. Giá hệ thống chứa WSE-1 vào khoảng vài triệu USD.

Tuy nhiên, các Big Chip không phải là không gặp thách thức. Dù có thể đạt được khả năng tính toán mạnh mẽ nhưng Big Chip vẫn phải đối mặt với các vấn đề về sản lượng, khả năng làm mát và hiệu suất.

Big Chip tạo ra nhiều nhiệt nên điều quan trọng là phải có hệ thống làm mát tốt và thiết kế sử dụng ít năng lượng hơn. Việc lập bản đồ nhiệm vụ và khám phá không gian thiết kế trong quá trình thiết kế Big Chip cũng là thách thức cần vượt qua”, Han Yinhe đề cập trong bài báo.